# EF-Train: Enable Efficient On-device CNN Training on FPGA Through Data Reshaping for Online Adaptation or Personalization

YUE TANG, University of Pittsburgh, USA XINYI ZHANG, University of Pittsburgh, USA PEIPEI ZHOU, University of Pittsburgh, USA JINGTONG HU, University of Pittsburgh, USA

Conventionally, DNN models are trained once in the cloud and deployed in edge devices such as cars, robots, or unmanned aerial vehicles (UAVs) for real-time inference. However, there are many cases that require the models to adapt to new environments, domains, or new users. In order to realize such domain adaption or personalization, the models on devices need to be continuously trained on the device. In this work, we design EF-Train, an efficient DNN training accelerator with a unified channel-level parallelism-based convolution kernel that can achieve end-to-end training on resource-limited low-power edge-level FPGAs. It is challenging to implement on-device training on resource-limited FPGAs due to the low efficiency caused by different memory access patterns among forward, backward propagation, and weight update. Therefore, we developed a data reshaping approach with intra-tile continuous memory allocation and weight reuse. An analytical model is established to automatically schedule computation and memory resources to achieve high energy efficiency on edge FPGAs. The experimental results show that our design achieves 46.99 GFLOPS and 6.09 GFLOPS/W in terms of throughput and energy efficiency, respectively.

CCS Concepts: • Hardware → Integrated circuits; Reconfigurable logic and FPGAs; Hardware accelerators.

Additional Key Words and Phrases: on-device training, edge FPGAs, data reshaping

#### 1 INTRODUCTION

Deep Neural Networks (DNNs) have been widely used in edge devices such as cars, robotics [5], and unmanned aerial vehicles (UAVs) [37], to accomplish various tasks, including autonomous driving, object detection, etc. FPGAs are promising platforms with higher computational density, communication bandwidth, and energy efficiency, and can be configured based on different tasks. Nowadays, FPGAs have been widely used in various edge device domains. For example, edge-scale FPGAs are commonly utilized in object detection tasks with high frames per second and low power consumption [8]. The Corazon-AI built on Xilinx Zynq is a perfect fit for various computer-vision-based applications including video surveillance, advanced driver-assistance systems (ADAS), medical robotics, industrial automation, and augmented reality [32]. Combined with reconfigurability, FPGAs have been adopted in several autonomous platforms such as pony.ai [33] and ZF ProAI [34]. In medical applications,

This work is supported by NSF CNS-2122320 Towards Unsupervised Learning on Resource Constrained Edge Devices with Novel Statistical Contrastive Learning Scheme.

Authors' addresses: Yue Tang, University of Pittsburgh, Pittsburgh, USA, yut51@pitt.edu; Xinyi Zhang, University of Pittsburgh, Pittsburgh, USA, xinyizhang@pitt.edu; Peipei Zhou, University of Pittsburgh, USA, peipei.zhou@pitt.edu; Jingtong Hu, University of Pittsburgh, Pittsburgh, USA, jthu@pitt.edu.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2022 Association for Computing Machinery. 1084-4309/2022/2-ART \$15.00

an FPGA-based low-latency multi-layer perception (MLP) processor for real-time cancer detection has been developed, since FPGA-based design can directly interface with sensors, display devices, and reduce data movement delays [25]. Burger et al. applied an FPGA-based embedded device to monitor usersâĂŹ electrocardiograms (ECGs) in a pervasive internet-of-things (IoT) system [1]. FPGAs have also been well performed in other areas such as agricultural robots [14], UAVs [40], etc. In traditional FPGA-based edge device applications, DNNs are pre-trained in the cloud before being deployed in FPGAs, which is not efficient for domain adaption. When the environments, tasks, or users change, data needs to be collected from the edge FPGAs and transmitted to the cloud. Then, the cloud retrains a new model, transmitting the model back to the edge devices. The whole process is inefficient and time-consuming. Therefore, it is often desirable for edge FPGAs to continuously and locally learn from new data. Such on-device learning can directly improve model accuracy and adapt to new environments. Currently, several algorithms have been proposed to enable edge devices to achieve domain adaption locally. For example, a MobileDA framework [36] has been developed to allow a novel teacher network trained in the server to distill the knowledge for a student network running in the edge device, and the algorithm was employed on an embedded GPU and NVIDIA Jetson TX2. A transductive transfer learning model HDCNN [13] has been proposed to allow adaptation without requiring collecting large volumes of labeled training data in the target domain, and the algorithm was tested on 1080 Ti GPU. To implement these complex and fantastic software-level algorithms on FPGA-based edge devices, an FPGA-based training accelerator is indispensable. However, traditional FPGA-based edge device applications lack such hardware-level designs for training operations, which prevents FPGA-based devices from applying these algorithms directly.

Furthermore, directly training Convolutional Neural Network (CNN) models on local FPGAs can facilitate personalization. For example, in some medical applications such as home monitoring [19], long-term ECG monitoring [24], etc., the distinction of different users' physical conditions will impact data distribution, so models need to be fine-tuned based on specific users. The system in [1] utilized cloud services to log a userâ $\check{A}$ Źs condition over time and continuously improve the systemâ $\check{A}$ Źs performance. It would be more effective if models could be directly updated on the FPGA device. Besides, learning at the edge can provide better privacy since users do not need to upload data into the central cloud [35].

However, it has been challenging to implement on-device training on FPGAs. Previous works mainly focused on implementing CNN inference on FPGAs. For example, Zhang et al. [38] exploited various optimization techniques including loop unrolling, loop tiling, and loop transformation on the FPGA accelerator, and proposed a roofline model to quantitatively analyze its computing throughput and required memory bandwidth. Various designs [31, 41] have been proposed to map well-trained neural networks on FPGAs for inference with high throughput and low latency. Compared with CNN inference, it is more complex to efficiently implement CNN training on FPGAs in terms of the following aspects. First, the inference process only includes forward propagation (FP), whereas the training process includes FP, backward propagation (BP), and weight update (WU), which leads to a 3X computation operation count with more types of operations [3]. Second, the large volume of activation data in FP needs to be used in BP and WU, and the loss data generated in BP is also required in WU. Such data dependency across multiple layers makes it difficult for on-board memory management and data reusing in dynamic random access memory (DRAM) in an end-to-end training system [27]. Third, since FP, BP, and WU have different memory access patterns, simply using the memory optimizations of FP in the whole training process leads to low memory access efficiency in BP and WU. Because of the above-mentioned challenges, CNN training on FPGAs has not been comprehensively investigated.

Recently, several FPGA-based architectures have been designed to accelerate training on large scale FPGAs. F-CNN [42] first performed FP and BP on a Maxeler MPC-X dataflow FPGA node but WU on CPU. Designs such as [18, 28] aimed to further reduce the CNN training latency and improve throughput. However, these works mainly focused on cloud-level devices with abundant resources. A straightforward training implementation on edge FPGAs is still challenging.

To tackle the challenges in implementing on-device training on edge-level FPGAs, we propose EF-Train, a new efficient FPGA-based training accelerator with a unified channel-level parallelism-based convolution kernel to handle the computation complexity. The unified kernel means that it processes convolution operations of FP, BP, and WU in the training phase utilizing the same computation resources on the FPGA chip. The channel-level parallelism means that the kernel allocates these computation resources to process multiple channels of feature maps in parallel. We also propose a data reshaping approach to solve the communication bottleneck in realistic end-to-end training processes. The overview of the design framework is shown in Fig. 1. The data reshaping approach is a compile-time optimization that achieves intra-tile and inter-tile memory access continuity and weight reuse in mini-batch training. The proposed design can be implemented on resource-limited FPGAs without sacrificing precision. Neural networks can be trained on both small batches and large batches. Since training and inference are conducted separately in realistic applications, and FPGAs are configurable to implement different designs on the same hardware platform for different applications, our design can be applied to those well-developed FPGA-based inference devices. In a relatively long life cycle of the inference phase, the original design can guarantee high throughput and low latency. If users or the environments change, the device can be switched to implement our design immediately to learn from local data for online adaptation or personalization rather than transmitting data to the cloud centers and waiting for the cloud centers to transmit the well-trained model back to the device. Our main contributions are as follows.

- We propose EF-Train, an efficient FPGA-based CNN training accelerator with a unified convolution kernel to process FP, BP, and WU with full precision. The accelerator exploits channel-level parallelism to achieve high computation utilization for both small and large batch sizes. Our accelerator supports end-to-end CNN training with convolutional (Conv) layers, fully connected (FC) layers, batch normalization (BN) layers, rectified linear unit (ReLU) layers, and pooling layers (Section 3).

- We propose a data reshaping approach to solve the off-chip communication bottleneck. The features and weights are stored in off-chip memory with intra-tile continuous memory allocation to remove discontinuous memory accesses within a tile. We also reduce inter-tile discontinuous memory accesses by scheduling loop orders between tiles. We further exploit weight reuse among multiple images in a mini-batch to improve communication efficiency when the batch size is larger than one (Section 4).

- We build a performance and resource model for the proposed accelerator. Based on the model, a computation and memory resources scheduling tool is established to determine design parameters for different FPGA devices and different neural networks (Section 5).

- We deploy the training process on PYNQ-Z1 and ZCU102 for various CNNs on both Cifar-10 and ImageNet datasets. Experimental results show that our design can achieve 46.99 GFLOPS and 6.09 GFLOPS/W in terms of throughput and energy efficiency, respectively (Section 6).

# **BACKGROUND AND MOTIVATIONS**

#### **CNN Training** 2.1

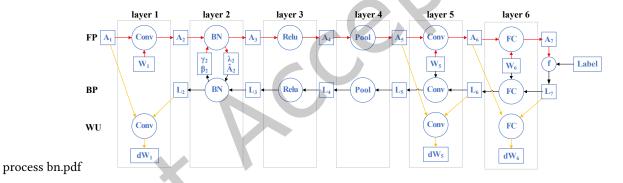

The training process of a five-layer CNN is shown in Fig. 2, including the FP process (red arrows), the BP process (black arrows), and the WU process (yellow arrows). The network includes two Conv layers, one FC layer, one BN layer, one ReLU layer, and one pooling layer which are practical and can make up most neural networks in real-world scenarios.

In the FP process, activation is propagated layer by layer. In a Conv layer such as layer 1, the input activation  $A_1$  conducts multiply-accumulate (MAC) operations with the weights  $W_1$ . A BN layer is always followed by a Conv layer. In layer 2, the inputs of the BN layer include the input activation  $A_2$  and learnable parameters  $\gamma_2$  and  $\beta_2$ . The immediate outputs include  $\lambda_2$ ,  $\hat{A}_2$ , and output activation  $A_3$ .  $A_3$  then goes through the ReLU and pooling layers. Finally, the FC layer provides classification results for the input image.

## Challenges for On-device Training on Edge-level FPGAs **Computation Complexity: Communication Bottleneck:** Involves FP, BP, and WU with more On-board memory management types of operations. difficulties. Low memory access efficiency in FP, BP, and WU **Unified Channel-level** Section 3 Parallelism-based Section 4 Data Reshaping Approach **Convolution Kernel Performance and Resource Model Section 5 Computation and Memory Resources Scheduling Tool**

Fig. 1. Overview of our design framework.

Fig. 2. CNN training process.

In the BP process, the loss will be calculated and propagated back to the first layer. The loss of the last layer is calculated by the loss function f. This paper adopts the most commonly used cross-entropy loss function. The stochastic gradient descent (SGD) is applied in CNN training. In a Conv layer, layer 5 for example, the loss  $L_6$  needs to be padded first to ensure the size of the convolution results  $L_5$  is the same as the size of  $A_5$ . The tensors for weights  $W_5$  are transposed on dimensions for output channels and input channels. The original kernel tensors need to be flipped. Then,  $L_5$  is calculated by the convolution operation between the transposed weights and  $L_6$ . In the maximum pooling layer, layer 4,  $A_4$  is compared with  $A_5$  to determine which element on  $L_4$  should obtain the value from the corresponding position on  $L_5$ . If layer 4 is an average pooling layer, the values for each element of each patch in  $L_5$  will be directly accumulated and propagated to  $L_4$ . In the ReLU layer, layer 3, an element of  $L_3$  will return zero if the value in the same position of  $A_3$  is less than zero. Otherwise, the value of the corresponding position in  $L_4$  will be propagated back. In the BN layer, layer 2,  $\gamma_2$  and  $\beta_2$  are updated according to the value of  $\lambda_2$ ,  $\hat{A}_2$ , and  $L_3$ . Then the loss is propagated back to  $L_2$ .

The gradients of weights in layer i is calculated after the loss of layer i + 1 is propagated. In layer 5,  $dW_5$  is calculated by conducting MAC operations for  $A_5$  and  $L_6$ . The gradients are accumulated inside a batch. In a mini-batch, after the above-mentioned operations are conducted for all images,  $W_5$  will be updated by subtracting  $dW_5 \times learning \ rate.$

#### 2.2 Related Works

DRAM Access Issues for Current FPGA-based Inference Accelerators: Currently, FPGAs have been widely adopted in edge domains thanks to the well-developed FPGA-based inference accelerators [38, 41]. Among the inference accelerators, many works [10, 12, 38] mainly focused on selecting optimal design parameters to improve the acceleration performance for individual Conv layers. Optimizing techniques such as loop tiling, loop unrolling are adopted by these works. Although the proposed algorithms achieved higher performance efficiency on a given Conv layer, the proposed designs only presented isolated accelerators without completing end-to-end inference where all layers of a neural network are tested continuously. In an end-to-end system, the layers' intermediate results are usually transferred between on-chip buffer and off-chip DRAM due to the limited on-chip storage size, so the impact of off-chip memory accesses should be considered in realistic scenarios. For most edge-level FPGAs, direct memory access (DMA) is a commonly used effective data swapping way for continuous address data reading. However, in current FPGA-based DNN deployments, when the on-chip memory cannot hold all the features and weights of a Conv layer, data need to be fetched and processed in tiles based on the computation pattern. Such tiling schemes break the continuity of data addresses in DRAM and thus reduce the DMA transmission efficiency. The detailed analysis will be further discussed in Section 4. This discontinuity can degrade the DMA transferring speed from about 8GB/s to around 1GB/s [6]. The optimal algorithms proposed in the above-mentioned accelerators are based on the assumption that data are well pre-allocated between adjacent layers so tiles can be loaded from and stored back to the DRAM continuously. However, in actual end-to-end systems, such allocation overhead is extremely large compared to the acceleration time.

Solutions for The DRAM Access Issues in The Inference Phase: Issues related to DRAM memory access have been addressed in recent works. For example, ROMANet [23] proposed a design space exploration (DSE) by searching for the appropriate data partitioning and scheduling for each layer of a network to reduce the number of memory accesses. DRMap [22] proposed a generic DRAM mapping policy and a DSE to reduce the DRAM access latency and energy. These two works were implemented on Tensor Processing Units (TPUs). [11] defined a multi-bank on-chip memory management (MOMM) problem to minimize the DRAM access overhead in the processing of CNNs on a neural processing unit (NPU) with a multi-bank on-chip memory. However, since FPGAs have different hardware architecture with TPUs or NPUs, their optimizing algorithms cannot be directly applied to FPGA-based designs. For example, in the TPU-based designs [22, 23], the architecture of the on-chip accelerator is already fixed, with fixed MAC arrays and fixed on-chip buffers for input features, output features, and weights, respectively. In FPGA-based designs, only the total number of DSPs and on-chip memory sizes are given, and the allocation and connection of MAC arrays and individual buffers are configured by the designer. Therefore, optimizations on FPGA-based designs should not only reduce DRAM access latency or frequency based on the off-chip DRAM access policy but also be comparable to support the on-chip acceleration designs.

A few FPGA-based works reorganized the DRAM layout to relieve the memory access discontinuity and validated the approaches on realistic end-to-end tests. For example, [6] compared three different layout schemes of input features in the inference phase and finally found that the channel-major scheme where the input features are fetched and stored along the input channel direction first could improve access continuity and reduce data duplication. Caffeine [39] combined both on-chip and off-chip data reorganizations for the convolutional matrixmultiplication representation to maximize the underlying memory bandwidth utilization. FlexCNNe [26] further optimized data layout optimizations on the concatenation layers.

However, all these works [6]-[26] are based on the computation and memory access pattern in the inference phase which only has FP. The training phase involves FP, BP, and WU where their data access pattern for output features, input features, and weights are different. Therefore, the above-mentioned approaches cannot be directly applied in CNN training, and a new optimized design considering FP, BP, and WU together is required.

**FPGA-based Training Accelerators:** As mentioned in Section 1, CNN training on FPGAs has not been comprehensively investigated. The training process is much more complicated than the inference process, so it is sub-optimal to directly adopt the frameworks of inference accelerators for training.

Due to the computation complexity and communication bottleneck, currently, only a few works aim to achieve efficient FPGA-based training. With FPGA clusters, FPDeep explored layer-level parallelism for training a CNN model in a fine-grained pipeline [30], which has superior scalability to a large number of FPGAs. However, such larger clusters are not suitable to be adopted on edge-level applications. For training on a single FPGA, an automatic compiler for training accelerator on Stratix 10 was developed in the precision of 16-bit fixed-point [28]. DarkFPGA adopted batch-level parallelism using 8-bit integers for training a VGG-like network on the Maxeler MAX5 platform [18]. It achieved high throughput when the batch size is large. A sparse CNN training accelerator was designed on VCU1525. The accelerator was implemented on a pre-trained CNN model with 85% parameters pruned [20]. However, these existing works mainly focused on cloud-level devices with abundant computation and memory resources.

Besides, even with cloud-level resources, reduced precision and pruning approaches have also been utilized to decrease computation intensity and communication bottleneck. Although quantization adopted in prior training accelerators [4, 18] led to remarkable benefits in terms of resource usage and power consumption, these works have not provided any evidence that such quantization techniques can remain high accuracy on a large dataset (e.g. ImageNet) with dense neural networks. Currently, training with full precision is still preferred in most realistic applications, and its high computation and memory overhead should be faced directly. However, none of the above-mentioned state-of-art training accelerators targeted resource-limited edge FPGAs with full precision, which is more challenging to implement end-to-end CNN training but is more practical in real-world scenarios. Therefore, an optimized design is necessary to implement on-device training on resource-limited FPGAs without sacrificing precision.

**Implementation of BN layers:** Apart from the computation-intensive Conv layer, the BN layer is also a key component and is essential for the training process. In inference, a BN layer can be folded into the adjacent CONV layer, since it just performs a simple linear transformation [17]. However, the batch normalization process in the training phase is much more complex. It needs to calculate the expected value and variance of the data in the whole mini-batch, which involves lots of on-chip and off-chip data transmission. Lu et al. [17] optimized the computation flow of BN layers during FP and BP, and implement BN layers in their CNN training accelerator. Unlike [17] which adopts the 8-bit fixed-point in Conv layers and FP16 in BN layers, our work supports BN layers with full precision, which brings more challenges for computation and transmission requirements.

## 2.3 Motivations of The Proposed Design

To implement on-device training on resource-limited FPGAs, we need to solve the computation complexity and communication bottleneck illustrated in Fig. 1.

In the training phase, the FP, BP, and WU processes are conducted iteratively and need to be completed on the same accelerator. Edge FPGAs have limited computational resources. Using separate kernels for FP, BP, and WU leads to resource underutilization and low energy efficiency. Therefore, to efficiently process the complex computation for FP, BP, and WU, we need to design a training accelerator that can handle the three processes in a unified convolution kernel and can achieve a high parallelism degree considering the flexibility of DNN architectures. For a Conv layer, there are three levels of parallelism that are adopted in FPGA-based accelerators:

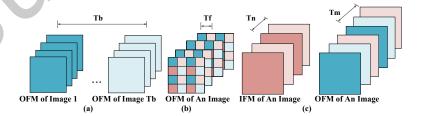

batch-level parallelism, feature-map-level parallelism, and channel-level parallelism. Fig. 3 (a) illustrates the process of batch-level parallelism, where Tb nominates the number of output feature maps (OFMs) of images in a mini-batch that are processed in parallel. Fig. 3 (b) shows the process of feature-map-level parallelism, where  $Tf \times Tf$  features of OFMs are processed in parallel. Fig. 3 (c) shows the process of channel-level parallelism, where Tm nominates the number of output channels of OFMs that are processed in parallel, and Tn nominates the number of input channels of input feature maps (IFMs) that are processed in parallel. The degree of parallelism depends on the amounts of utilized computation units on the hardware. Table 1 shows the comparisons of the three levels of parallelism. Considering a Conv layer with B images in a mini-batch, it is assumed that the number of input channels is N, the number of output channels is M, the size of an OFM is  $R \times C$ , and the size of a weights kernel is  $K \times K$ .  $Tmops = B \times M \times N \times R \times C \times K \times K$  multiply operations are required to process such a layer. For the batch-level parallelism, it takes  $\lceil \frac{B}{Th} \rceil \times M \times N \times R \times C \times K \times K$  cycles to complete the Conv layer. Such parallelism can achieve high throughput when the batch size is large, and the size of the feature map and the number of channels have little impact on the performance. For example, in previous works, DarkFPGA [18] built its accelerator with batch-level parallelism and achieved high throughput when the batch size is 128. However, when the batch size is small or even 1 (online learning), most computation units will remain idle. For example, when B < Tb, completing the Conv layer costs Tmops cycles, and  $\frac{Tb-B}{Tb}$  of computation resources remain idle. It leads to a low parallelism degree and such under-utilization of resources makes the performance sub-optimal. For the feature-map-level parallelism which has been adopted by works like [28], it takes  $B \times M \times N \times \lceil \frac{R}{Tf} \rceil \times \lceil \frac{C}{Tf} \rceil \times K \times K$  cycles to finish a Conv layer. The batch size and the number of channels have little impact on such parallelism. The parallelism will benefit from layers with large feature map size but has under-utilization for layers with small feature map size. For example, when R < Tf and C < Tf, completing the Conv layer costs Tmops cycles, and  $\frac{Tf - R}{Tf} \times \frac{Tf - C}{Tf}$  of computation resources will remain idle. However, in CNN training, the size of a feature map may vary from large size (like  $224 \times 224$  for the input image of the ImageNet) to  $1 \times 1$  for the FC layer. The feature-map-level parallelism will be inefficient to process the layers with a small feature map. For channel-level parallelism, it takes  $B \times \lceil \frac{M}{Tm} \rceil \times \lceil \frac{N}{Tn} \rceil \times R \times C \times K \times K$  cycles to complete the Conv layer. It acquires a high parallelism degree with a large channel number, and the batch size and feature map size have little impact on it. When the channel number is small, for example, when N < Tn, completing the Conv layer costs  $B \times \lceil \frac{M}{Tm} \rceil \times N \times R \times C \times K \times K$  cycles, and  $\frac{T_{n-N}}{T_n}$  of computation resources will remain idle. However, for most neural networks, only the first layer has a small input channel number (N = 3). For other layers, the channel size (for example 32, 64, etc.) is usually larger than the maximum degree of parallelism that an edge FPGA can achieve. Therefore, channel-level parallelism is widely adopted by FPGA-based inference accelerators [10, 38]. Generally speaking, the channel-level parallelism can achieve a constantly high degree of parallelism across multiple layers, so it is adopted in the proposed design as shown in Fig. 1. The proposed accelerator with a channel-level parallelism-based convolution kernel to process FP, BP, and WU will be introduced in detail in Section 3.

Fig. 3. Three levels of parallelism. (a) Batch-level parallelism, (b) Feature-map-level parallelism, (c) Channel-level parallelism.

| 8 • | Tang | and | Hu, | et | a |

|-----|------|-----|-----|----|---|

|-----|------|-----|-----|----|---|

| Parallelism            | Batch-level<br>Parallelism | Feature-map-level<br>Parallelism | Channel-level<br>Parallelism |

|------------------------|----------------------------|----------------------------------|------------------------------|

| Large Batch Size       | advantaged                 | little impact                    | little impact                |

| Small Batch Size       | disadvantaged              | little impact                    | little impact                |

| Large Feature Map Size | little impact              | advantaged                       | little impact                |

| Small Feature Map Size | little impact              | disadvantaged                    | little impact                |

| Large Channel Number   | little impact              | little impact                    | advantaged                   |

| Small Channel Number   | little impact              | little impact                    | disadvantaged                |

|                        |                            |                                  |                              |

Table 1. Comparisons of the three levels of parallelism

Furthermore, the communication bottleneck is also challenging for edge-level FPGAs in end-to-end training. As illustrated in Fig. 2, the activation data in FP needs to be used in BP and WU, and the loss data generated in BP is also required in WU. The length and heterogeneity of the data dependency paths in different layers make external memory accesses inevitable [27]. Previous training accelerators attempted to avoid external memory accesses. For example, FPDeep [30] scaled CNN computations to larger clusters so that only on-chip memory is needed for the CONV layers. However, such larger clusters cannot be used on edge devices. [16] implemented LeNet-10 on an FPGA and stored the inputs and outputs of one layer on the chip. Such design can only support small networks, but for many larger networks (e.g. Vgg-16, AlexNet, etc.), the on-chip memory of an edge FPGA is not big enough to hold weights or features in every Conv layer. Therefore, several works [4, 18, 20] applied quantization or pruning to reduce off-chip memory access. However, unlike inference where compressed networks cause little accuracy decrease [7], these training works have not proved that their compression techniques can remain high accuracy on large datasets with dense networks. To guarantee accuracy, it is necessary to implement CNN training with full precision. Our goal is to design a general accelerator supporting end-to-end training with both dense and small networks without sacrificing precision, so it is necessary to appropriately manage external memory access and allocate on-chip buffers. As mentioned in Section 2.2, the tiling schemes involved in on-chip accelerator design break the continuity of data addresses in DRAM and thus reduce the DMA transmission efficiency. Therefore, it is necessary to improve the address continuity of data to improve the efficiency of data swapping considering the complex data patterns in FP, BP, and WU altogether. To solve this communication issue, as shown in Fig. 1, a data reshaping approach is proposed and will be introduced in detail in Section 4.

### FPGA-BASED CNN TRAINING ACCELERATOR

In this section, we propose an FPGA-based accelerator exploiting channel-level parallelism to deal with the training process. A unified convolution kernel is designed to process FP, BP, and WU with full precision.

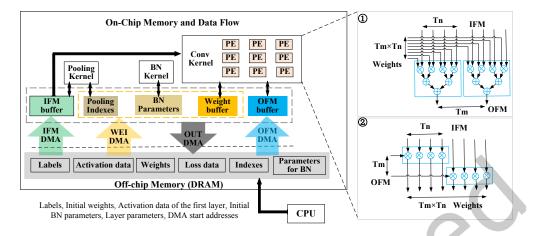

## The Architecture of The Training Accelerator

The proposed training accelerator is shown in Fig. 4. We implement our accelerator on an end-to-end training system. At first, the CPU transmits labels, initial weights, the activation data of the first layer, layer parameters, initial parameters for BN layers, and the DMA start addresses for each layer to the off-chip DRAM. The layer parameters include computation type (e.g. Conv, ReLU, BN, or pooling) and the shape information. The DMA start addresses are calculated off-line according to the off-chip memory layout based on our data reshaping approach mentioned in Section 4. Our accelerator executes computation-intensive kernels based on data dependencies within a CNN model, while the entropy loss function is computed on the off-chip ARM core.

Fig. 4. Accelerator architecture.

As illustrated in Fig. 4, the off-chip memory (DRAM) stores data for activation, loss, weights, labels, indexes for pooling, and parameters for BN. Data are transmitted through the DMA AXI-stream bus to on-chip memory for computation. There are 4 DMA stream channels: IFM DMA, OFM DMA, WEI DMA, and OUT DMA. These 4 channels are independent and can work in parallel. On the FPGA chip, a unified Conv kernel is designed to process FP, BP, and WU with the same computation resources, i.e. the digital signal processors (DSPs). The Conv kernel is composed of multiple processing elements (PEs) to implement MAC operations. The adder tree structure is adopted for the proposed kernel since it is flexible to support different computation patterns for FP, BP, and WU. The connection of each multiplier and adder for FP and BP is shown in ① of Fig. 4, while the connection of each multiplier and adder for WU is shown in ② of Fig. 4. The Pooling Kernel focuses on the pooling operation. The BN Kernel achieves batch normalization and updates BN parameters during FP and BP. ReLU is always followed by a Conv or BN layer. The accelerator compares the output features with 0 when storing output features back to the DRAM in Conv or BN layers, so ReLU does not need a unique functional unit. Five types of on-chip block RAMs (BRAMs) are used to buffer IFMs, weights or weights gradients, OFMs, pooling indexes, and BN parameters. We adopt double-buffer designs so that data transmission and computation can be conducted in parallel.

## 3.2 The Forward and Backward Propagation of A Convolutional Layer

Our accelerator adopts channel-level parallelism, loop unrolling, and loop tiling. The symbols are defined in Table 2. In channel-level parallelism, Tn and Tm are determined by available computation resources (i.e. DSPs) on the FPGA chip and are fixed for all Conv layers. The degree of parallelism is determined by  $Tn \times Tm$ .

Our accelerator achieves SGD in CNN training. The forward and backward propagation processes of a Conv layer processing the bth image in a mini-batch can be formulated in Eq. (1) and (2), where  $W_i'$  is the transposed and flipped tensor of  $W_i$ . As illustrated in ① of Fig. 4, in FP and BP, the Conv Kernel conducts MAC operations for weights and input features from activation or loss. The IFM buffer stores a tile of activation or loss transmitted via the IFM DMA channel, and the Weight buffer stores weights transmitted via the WEI DMA channel. The OFM buffer stores a tiled of MAC outcomes. Computation results are transmitted to the DRAM via the OUT DMA channel. If a Conv layer is followed by a ReLU layer, for FP, the data in the OFM buffer will be compared with 0 before entering into the OUT DMA channel. For BP, the activation of the previous layer will be transmitted via

Table 2. Definitions of Symbols

| Notation             | Description                                                                      |

|----------------------|----------------------------------------------------------------------------------|

| i,j                  | Index of a Conv layer                                                            |

| B                    | Batch size                                                                       |

| $N^i$                | Number of the input channels of the <i>i</i> th Conv layer                       |

| $M^i$                | Number of the output channels of the <i>i</i> th Conv layer                      |

| $R^i$                | Number of the rows of the OFMs for the <i>i</i> th Conv layer                    |

| $C^{i}$              | Number of the columns of the OFMs for the <i>i</i> th Conv layer                 |

| $K^i$                | Size of the weights kernel for the <i>i</i> th Conv layer                        |

| $S^i$                | Stride for the <i>i</i> th Conv layer                                            |

| $A_i[b, m, r, c]$    | Activation for the <i>i</i> th Conv layer in FP                                  |

| $L_i[b,n,r,c]$       | Loss for the <i>i</i> th Conv layer in BP                                        |

| $W_i[n, m, kr, kc]$  | Weights for the <i>i</i> th Conv layer                                           |

| $dW_i[n, m, kr, kc]$ | Weights gradients for the <i>i</i> th Conv layer in WU                           |

| Tm                   | Number of the output channels in a tile of output features                       |

|                      | in each Conv layer                                                               |

| Tn                   | Number of the input channels in a tile of input features in                      |

|                      | each Conv layer                                                                  |

| $Tr^i$               | Number of the rows in a tile of output features in the <i>i</i> th Conv layer    |

| $Tc^i$               | Number of the columns in a tile of output features in the <i>i</i> th Conv layer |

| $M^i$ _on            | Number of the output channels of the weights that stored on-chip in              |

|                      | the <i>i</i> th Conv layer                                                       |

| $R^j$ _in            | Number of the rows of the IFMs for the <i>j</i> th Conv layer                    |

| $C^j$ _in            | Number of the columns of the IFMs for the <i>j</i> th Conv layer                 |

| Tr <sup>j</sup> _in  | Number of the rows in a tile of input features in the <i>j</i> th Conv layer     |

| Tc <sup>j</sup> _in  | Number of the columns in a tile of input features in the <i>j</i> th Conv layer  |

the OFM DMA channel, and the accelerator decides which value should be propagated according to Eq. (3).

$$A_{i+1}[b, m, r, c] = \sum_{n=1}^{N^i} \sum_{kr=1}^{K^i} \sum_{kc=1}^{K^i} A_i[b, n, S^i \times r + kr, S^i \times c + kc] \times W_i[m, n, kr, kc]$$

(1)

$$L_{i}[b, n, r, c] = \sum_{m=1}^{M^{i}} \sum_{kr'=1}^{K^{i}} \sum_{kc'=1}^{K^{i}} L_{i+1}[b, m, S^{i} \times r + kr', S^{i} \times c + kc'] \times W'_{i}[n, m, kr', kc']$$

(2)

$$L_{i}[b, m, r, c] = \begin{cases} L_{i+1}[b, m, r, c], & A_{i}[b, m, r, c] > 0, \\ 0, & others \end{cases}$$

(3)

## 3.3 The Weight Update of A Convolutional Layer

The gradients of weights can be calculated in Eq. (4). The generated hardware implementation of the PE architecture processing WU operations in the Conv kernel is shown in ② of Fig. 4. During the WU, the Conv Kernel conducts MAC operations for the activation data transmitted via the IFM DMA channel and the loss data transmitted via the OFM DMA channel. The gradients are stored in the Weight buffer. Once the Conv Kernel

completes the computation for the last image in a mini-batch, the original weights are transmitted via the WEI DMA channel. Then, weights are updated by deducting the product of the gradients and learning rate. New weights are sent back to DRAM via the OUT DMA channel.

$$dW_{i}[m, n, kr, kc] = \sum_{b=1}^{B} \sum_{r=1}^{R^{i}} \sum_{c=1}^{C^{i}} L_{i+1}[b, m, r, c] \times A_{i}[b, n, S^{i} \times r + kr, S^{i} \times c + kc]$$

$$(4)$$

## The Forward and Backward Propagation of A Pooling Layer

In the FP process of a pooling layer, the activation is transmitted via the IFM DMA channel and stored in the IFM buffer. In the maximum pooling, the Pooling Kernel compares adjacent pixels, transfers the results back to DRAM via the OUT DMA channel, and records the index for the maximal pixel into the Pooling Indexes buffer. The index of a pixel is a 2-bit integer. For average pooling, the kernel just calculates the average value of a patch of features. In the BP process of maximum pooling, the indexes are loaded back via the WEI DMA channel, and loss from the previous layer is loaded via the IFM DMA channel. The Pooling Kernel compares the indexes and stores the propagated value into the IFM buffer. The BP process of the maximum pooling is formulated in Eq. (5). For average pooling, the loss values of a patch are directly accumulated. After a tile of data is processed, the calculated loss is sent back via the OUT DMA channel.

$$L_{i}[b, m, S^{i} \times r + kr, S^{i} \times c + kc] = \begin{cases} L_{i+1}[b, m, r, c], A_{i+1}[b, m, r, c] = A_{i}[b, m, S^{i} \times r + kr, S^{i} \times c + kc], \\ 0, others \end{cases}$$

(5)

#### The Forward Propagation of A BN Layer 3.5

Our BN kernel is based on the computation flow in [17]. However, unlike the prior work which utilizes halfprecision, we adopt full precision which brings more computation and transmission challenges. The BN parameters in Fig. 4 includes learnable parameters  $\gamma_i[m]$  and  $\beta_i[m]$  and immediate parameters  $\lambda_i[m]$  and  $\hat{A}_i[b, m, r, c]$ , where m is the index of the channel. The  $\gamma_i[m]$  and  $\beta_i[m]$  are used to generate the immediate parameters and the output activation  $A_{i+1}[b, m, r, c]$  during FP. During BP, the immediate parameters and the loss propagated from the next layer  $L_{i+1}[b, m, r, c]$  are used to update the learn parameters and propagate the loss  $L_i[b, m, r, c]$  back. Since the size of  $\gamma_i[m]$ ,  $\beta_i[m]$ , and  $\lambda_i[m]$  is M (the number of the output channels), the on-chip BRAMs are large enough to hold these data in a BN layer. Therefore, we use the BN Parameters buffer to store these parameters as well as the expected value and variance. The  $\hat{A}_i[b, m, r, c]$  is transmitted to DRAM together with  $A_{i+1}[b, m, r, c]$ .

In FP, the BN Kernel first loads  $\gamma_i[m]$  and  $\beta_i[m]$  from DRAM to the BN Parameters buffer via the WEI DMA channel. Then it loads  $A_i[b, m, r, c]$  via the IFM DMA channel and calculates the expected value  $E(X)_i[m]$  and variance  $V(X)_i[m]$  according to Eq. (6)-(8). To avoid disarranging the DRAM data layout for adjacent Conv layers, we load data tile by tile using the same data format as that in Conv layers. The expected value and variance are calculated after the entire data of a mini-batch is accessed. Then input activation is loaded from the beginning to calculate the immediate parameters according to Eq. (9) and Eq. (10), where  $\epsilon$  is a constant parameter.  $\lambda_i[m]$  is stored in the BN Parameters buffer, while  $\hat{A}_i[b, m, r, c]$  is transmitted to DRAM via the OUT channel in parallel with activation loading. Finally, the output activation is calculated according to Eq. (11). The BN operation completes after the activation,  $\gamma_i[m]$ ,  $\beta_i[m]$ , and  $\lambda_i[m]$  are stored to DRAM.

$$E(X)_{i}[m] = \frac{1}{B \times R^{i} \times C^{i}} \sum_{b=1}^{B} \sum_{r=1}^{R^{i}} \sum_{c=1}^{C^{i}} A_{i}[b, m, r, c]$$

(6)

$$E(X^{2})_{i}[m] = \frac{1}{B \times R^{i} \times C^{i}} \sum_{b=1}^{B} \sum_{r=1}^{R^{i}} \sum_{c=1}^{C^{i}} A_{i}^{2}[b, m, r, c]$$

(7)

$$V(X)_{i}[m] = E(X^{2})_{i}[m] - (E(X)_{i}[m])^{2}$$

(8)

$$\lambda_i[m] = \frac{1}{\sqrt{V(X)_i[m] + \epsilon}} \tag{9}$$

$$\hat{A}_{i}[b, m, r, c] = (A_{i}[b, m, r, c] - E(X)_{i}[m]) \times \lambda_{i}[m]$$

(10)

$$A_{i+1}[b, m, r, c] = \hat{A}_i[b, m, r, c] \times \gamma_i[m] + \beta_i[m]$$

(11)

### 3.6 The Backward Propagation of A BN Layer

In BP,  $\hat{A}_i[b, m, r, c]$ ,  $\lambda_i[m]$  and  $L_{i+1}[b, m, r, c]$  are used to update the learnable parameters  $\gamma_i[m]$  and  $\beta_i[m]$ , and  $L_i[b, m, r, c]$  is propagated back.  $\lambda_i[m]$ ,  $\gamma_i[m]$ , and  $\beta_i[m]$  are first uploaded via the WEI channel and stored in the BN Parameters buffer. Then, the BN Kernel loads  $\hat{A}_i[b, m, r, c]$  and  $L_{i+1}[b, m, r, c]$  via the IFM and OFM channel respectively to calculate the gradients for  $\gamma_i[m]$  and  $\beta_i[m]$  according to Eq. (12) and (13). The learnable parameters are updated by deducting the gradients, while  $L_i[b, m, r, c]$  is calculated according to Eq. (14).

$$d\gamma_i[m] = \sum_{h=1}^B \sum_{r=1}^{R^i} \sum_{c=1}^{C^i} L_{i+1}[b, m, r, c] \times \hat{A}_i[b, m, r, c]$$

(12)

$$d\beta_i[m] = \sum_{b=1}^B \sum_{r=1}^{R^i} \sum_{c=1}^{C^i} L_{i+1}[b, m, r, c]$$

(13)

$$L_{i}[b, m, r, c] = \gamma_{i}[m] \times \lambda_{i}[m] \times (L_{i+1}[b, m, r, c] - \frac{d\beta_{i}[m]}{B \times R^{i} \times C^{i}} - \hat{A}_{i}[b, m, r, c] \times \frac{d\gamma_{i}[m]}{B \times R^{i} \times C^{i}})$$

(14)

#### 4 DATA RESHAPING APPROACH

In this section, we propose a data reshaping approach to solve the communication bottleneck between the on-chip buffer and off-chip memory in realistic end-to-end training processes. We first analyze the discontinuous memory access for the isolate accelerator with the unified channel-level parallelism-based Conv kernel proposed in Section 3. Then we introduce our data reshaping approach which involves three aspects. We first achieve intra-tile continuous memory allocation by reorganizing the DRAM layouts for input features, output features, and weights. Then, we re-schedule the loop order to achieve inter-tile continuous memory allocation. These two parts are optimized together. Finally, considering the training process involves convolution operations among a mini-batch, we propose and apply a weight reuse strategy based on the proposed data layout.

#### 4.1 Analysis on Discontinuous Memory Access

The pseudo-code of a tiled convolution layer is shown in Fig. 5. The pseudo-code in Fig. 5 (a) is applied in FP and BP, following previous FPGA-based inference works [38, 39], while the pseudo-code in Fig. 5 (b) is applied in WU, based on the accelerator design proposed in Section 3. As discussed in Section 2, the continuity of data significantly influences the DMA transmission efficiency. In this section, we analyze the data discontinuity when features are placed with the BCHW pattern and the BHWC pattern, where B represents batch, C represents channel, H represents height (row), and W represents width (column).

| Off-chip data transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Off-chip data transmission                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. for (row=0; row <r; (col="0;" (ti="0;" (to="0;" 2.="" 3.="" 4.="" col+="Tc){" col<c;="" for="" row+="Tr){" ti+="Tn){&lt;/td" ti<n;="" to+="Tm){" to<m;=""><td>1. for (to=0; to<m; 2.<="" td="" to+="Tm){"></m;></td></r;>                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1. for (to=0; to <m; 2.<="" td="" to+="Tm){"></m;>                                                                                                                                                                                                                                                   |

| On-chip computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | On-chip computation                                                                                                                                                                                                                                                                                  |

| $ \begin{array}{ll} 5. \; & \text{for}(i=0; \; i \!\!<\!\! K; \; i \!\!+\!\!\!+\!\!\! \} \\ 6. & \text{for}(j=0; \; j \!\!<\!\! K; \; j \!\!+\!\!\!+\!\!\! \} \\ 7. & \text{for}(ttr=0; \; ttr \!\!<\!\! Tr; \; ttr \!\!+\!\!\!+\!\!\! \} \\ 8. & \text{for}(tcc=0; \; tcc \!\!<\!\! Tc; \; tcc \!\!+\!\!\! +\!\!\! ) \{ \\ 9. & \text{for}(too=0; \; too \!\!<\!\! Tm; \; too \!\!+\!\!\! +\!\!\! ) \{ \\ 10. & \text{for}(tii=0; \; tii \!\!<\!\! Tn; \; tii \!\!+\!\!\! +\!\!\! ) \{ \\ OFM[too][ttr][tcc] \!\!+\!\!\! = \\ WEI[too][tii][i][j]^*IFM[tii][S^*ttr \!\!+\!\! i][S^*tcc \!\!+\!\! j] \\ \}\}\}\}\}\}\} \} \} \} \} \} \} \} \} \} \} \} \} \} \} $ | 5. for(trr=0; trr <tr; +="OFM[too][trr][tcc]*IFM[tii][S*trr+i][S*tcc+j]" 10.="" 6.="" 7.="" 8.="" 9.="" for(i="0;" for(tcc="0;" for(tii="0;" for(too="0;" i++)="" i<k;="" tcc++)="" tcc<tc;="" td="" tii++)="" tii<tr;="" too++)="" too<tr;="" trr++)="" wei[too][tii][i][j]="" {="" }}}}<=""></tr;> |

| (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (b)                                                                                                                                                                                                                                                                                                  |

Fig. 5. Pseudo-code of a tiled convolution layer. (a) Pseudo-code for FP and BP, (b) Pseudo-code for WU.

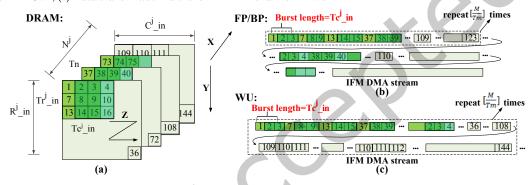

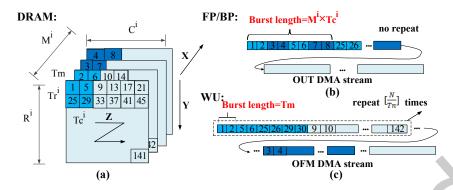

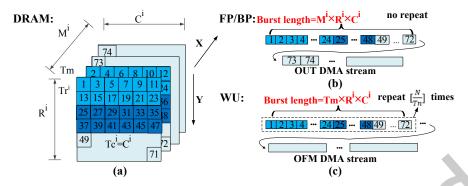

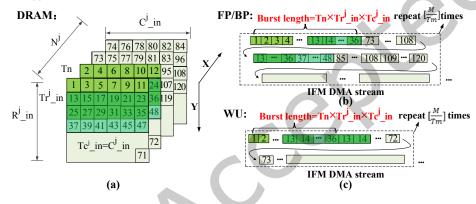

**Features are placed in the BCHW pattern:** Fig. 6 (a) shows the data layout of  $M^i \times R^i \times C^i$  output features stored in DRAM for the *i*th layer. The output features are placed with the BCHW pattern commonly used in CNN accelerating CPU, and GPU platforms [2, OpenVINO]. While OpenVINO [OpenVINO] is primarily for CPUs, it would also work for CPU, GPU, and FPGA platforms. In this layout, a cube represents an element of the features, and the indexes represent the orders of the elements stored in DRAM. In FPGA-based DNN deployments, data are fetched and processed in tiles. As shown in Fig. 6, the size of a tile is  $Tm \times Tr^i \times Tc^i$  for output features.

The output features of layer i are also the input features for its next layer j. As shown in Fig. 7 (a), the size of the input features in layer j is  $N^j \times R^j in \times C^j in$ . For input features, the size of a tile is  $Tn \times Tr^j in \times Tc^j in$ .

In each DMA stream, the AXI-stream bus allows a pipeline data stream when the data addresses are continuous. Burst length represents the number of data with continuous addresses in the data stream. When a discontinuity happens, the DMA needs to be restarted. Therefore, our goal is to avoid discontinuity, i.e. elongate the burst length for different transmission patterns.

During FP, the Conv Kernel conducts MAC operations with weights and input features, and then it generates output features. The output features are transmitted to the DRAM via the OUT DMA channel, which is shown in Fig. 6 (b). For the next layer, the input features are fetched from DRAM to the FPGA chip via the IFM DMA stream, which is shown in Fig. 7 (b). As illustrated in Fig. 5 (a), in a Conv layer, the OFM buffer is reused to store and accumulate the immediate convolution results between each tile of input features and each tile of weights. The first tile of output features is generated by accumulating the convolution results when the input features tiles move from the first input channel to the last channel. It corresponds to the movement in the **X** direction in Fig. 7. Then, the next tiles of output features are generated in the **X** direction in Fig. 6, so the data access pattern of input features (the dashed box in Fig. 7 (b)) repeats  $\lceil \frac{M}{Tm} \rceil$  times. After the output features tiles move from the first output channel to the last output channel, they begin to move in the **Z** direction, and the input features tiles

follow the Z direction as well. From Fig. 6 (b) and Fig. 7 (b), the address of data is discontinuous for both inside and outside of a tile. The burst length of the output features in the ith layer is  $Tc^i$ , and the burst length of the input features in the jth layer is  $Tc^{j}$  in. The data movement in BP is similar to that in FP. In WU, the data access pattern inside a tile is the same as that in FP/BP. However, the inter-tile data access pattern is different from that for FP/BP. It is because, in WU, the Conv Kernel conducts MAC operations for input features (the activation data transmitted via the IFM DMA channel) and output features (the loss data transmitted via the OFM DMA channel) to calculate weight gradients. Therefore, as shown in Fig. 5 (b), the WEI buffer is reused to store and accumulate the immediate convolution result between each tile of input features and each tile of output features. The first tile of weight gradients is generated when the input and output features tiles move from the first row and the first column to the last row and the last column. It corresponds to the movement in the Z direction in Fig. 6 and Fig. 7. Then, the next tile of weight gradients is generated along the input channel direction. The tiles of input features move along the X direction, while the pattern of output feature tiles (the dashed box in Fig. 6 (c)) repeats  $\lceil \frac{N}{T_n} \rceil$ times. After the gradients of weights are calculated from the first input channel to the last input channel, the next tiles are generated along the output channel direction. Thus, the pattern of input feature tiles (the dashed box in Fig. 7 (c)) repeats  $\lceil \frac{M}{Tm} \rceil$  times, while the output feature tiles move along the X direction. As shown in Fig. 7 (c), the burst length for input features is  $Tc^{j}$ \_in. As shown in Fig. 6 (c), the burst length for output features is  $Tc^{i}$ .

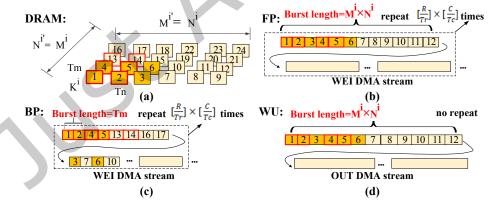

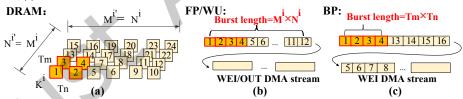

In CNN training, the data layout of weights is also more complex compared to the inference process. As illustrated in Fig. 8 (a),  $M^i \times N^i \times K^i \times K^i$  weights of layer i are stored in DRAM. In FP, weights are fetched in the input channel first and then the output channel when the output features are generated along the **X** direction in Fig. 6. Then, the output features are generated along the **Z** direction, while the weights access pattern (the dashed box in Fig. 8 (a)) repeats  $\lceil \frac{R}{T_r} \rceil \times \lceil \frac{C}{T_c} \rceil$  times. WU shares the same intra-tile weights access pattern with FP, but it does not need to repeat during inter-tile data access. The burst lengths for FP and WU are both Tn. In BP, each  $K^i \times K^i$  kernel needs to be flipped. Such reallocation can be processed on the FPGA chip. However, since the numbers of input channels and output channels are interchanged, the memory access pattern of a tile is also changed. The weights kernels are transposed between the input channel dimension and the output channel dimension. In Fig. 8, the yellow cubes represent a tile of weights in FP and WU, and the cubes with the red box represent a tile of weights in BP. As illustrated in Fig. 8 (c), in BP, the number of output channels becomes  $M^{i'} = N^i$ , the number of input channels becomes  $N^{i'} = M^i$ , and the burst length is Tm.

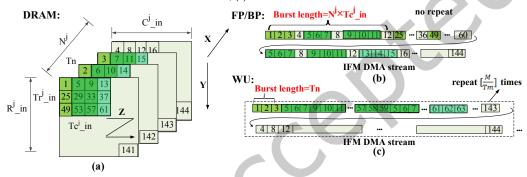

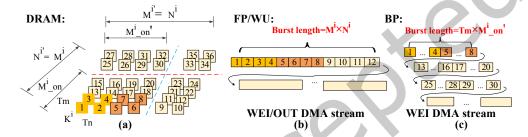

**Features are placed in the BHWC pattern:** As can be seen from Fig. 6, Fig. 7, and Fig. 8, the tiled data breaks the data continuity of memory access in FP, BP, and WU for the isolate accelerator. In FPGA-based inference works, the BHWC pattern is also commonly used in end-to-end designs to optimize memory access [6, 39]. Fig. 9 (a) and Fig. 10 (a) show the data layout of features placed in the BHWC pattern following previous inference-based works. According to the loop order in Fig. 5 (a), in FP and BP, tiles move in the channel dimension first and then move in the **Z** direction. Therefore, it is effective to fetch  $\lceil \frac{N}{Tn} \rceil$  tiles of input features to the on-chip memory and reuse the data after  $\lceil \frac{M}{Tm} \rceil$  tiles of output features are calculated. With such optimizations, the data discontinuity of features is alleviated in FP and BP. As shown in Fig. 9 (b) and Fig. 10 (b), the burst length for output features is  $M^i \times Tc^i$ , and the burst length for input features is  $N^j \times Tc^j$ \_in. Besides, the FPGA accelerator does not need to repeatedly load the input feature tiles from the DRAM.

However, in WU, the Conv Kernel conducts MAC operations for input features and output features to calculate weight gradients, so input and output feature tiles should move in the **Z** direction first to calculate the weight gradients of  $Tm \times Tn$  weights kernels and then move in the channel direction, which is illustrated in Fig. 5 (b). Therefore, features cannot be continuously fetched to the on-chip buffer and reused as that in the inference phase unless the on-chip memory is large enough to hold all features of each layer. When the on-chip memory cannot hold all features of a Conv layer in resource-limited FPGAs, the burst length for output features is Tm, and the burst length for input features is Tn. The data layouts are shown in Fig. 9 (c) and Fig. 10 (c).

In CNN inference, weights will not change in the whole process, and they are loaded in the same pattern for different layers. Therefore, in the inference phase, weights can be pre-allocated tile by tile to ensure continuous memory access. The pre-allocated data layout is illustrated in Fig. 11 (a). As shown in Fig. 11 (b) and Fig. 11 (d), the burst length is  $M^i \times N^i$  in FP and WU. However, as illustrated in Fig. 11 (c), the weight kernels are transposed between the input channel dimension and the output channel dimension, and the tiling scheme in BP breaks the memory access continuity. Since weights are updated after one iteration of FP, BP, and WU, it is impossible to pre-allocate them before each iteration. Therefore, data discontinuity is inevitable in BP. As shown in Fig. 11, the burst length is Tm.

## 4.2 Optimizing Discontinuous Memory Access

To optimize the discontinuous memory access, our data reshaping approach includes the following steps. Firstly, we achieve intra-tile continuous memory allocation for both features and weights by reorganizing the DRAM layouts for output features, input features, and weights which are shown in Fig. 12, Fig. 13, and Fig. 14 respectively. Then we schedule the loop order based on the pseudo-code in Fig. 15 to achieve inter-tile continuous memory allocation. Finally, weights are reused among a mini-batch based on the proposed data layouts. In this section, we reorganize the data layouts and schedule the loop order together to achieve both intra-tile and inter-tile continuous memory address allocation.

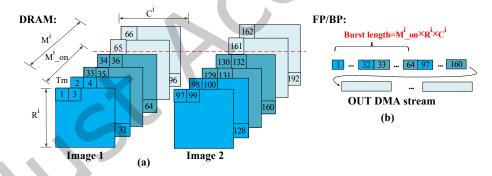

Intra-Tile Continuous Memory Allocation: Inspired by previous inference works [6, 39], employing channel-last data layout can improve data continuity for the channel-level parallelism-based accelerator. However, as explained in Section 4.1, simply changing the data layout cannot optimize the memory access continuity in FP, BP, and WU together. The memory access patterns in the three processes need to be considered together. In CNN inference, the selection of Tm and Tn is flexible. However, to ensure data continuity of weights kernels in both FP and BP, we fix Tm = Tn in our training accelerator so that weights can be loaded tile by tile in both FP and BP. Fig. 12 (a) shows the data layout of the output features in DRAM after data reshaping. The first Tm channels of OFMs are placed in the row-column-channel pattern. The next Tm channels of OFMs are followed with the same pattern. When applying loop tiling, we assign the tiling parameter  $Tc^i = C^i$  so that data are continuous inside a tile for both FP and WU. From Fig. 12 (b) and (c), the burst lengths of output features during FP, BP, and WU are larger than the size of a tile.

The selection of Tm = Tn,  $Tc^i = C^i$ , and  $Tc^i_-in = C^i_-in$  also guarantee that features of different layers share similar data layouts and tiling schemes no matter they serve as output features or input features of a Conv layer in FP/BP/WU. Therefore, the intra-tile continuity of input features is also guaranteed. The data layout of the input features in DRAM for the jth layer is shown in Fig. 13 (a). According to Fig. 13 (b) and (c), the burst length equals the size of a tile.

After selecting Tm = Tn, weights can be placed and fetched tile by tile during FP, BP, and WU. The data layout is illustrated in Fig. 14. Before data reshaping, weights need to be repeatedly transmitted between the FPGA chip and the DRAM in FP and BP, which is inefficient especially for mini-batch training. Therefore, weight reuse based on our unique data layout is necessary which will be introduced in detail in Section 4.3. After reshaping, the burst length for FP and WU is  $M^i \times N^i$ , while the burst length for BP is  $Tm \times Tn$ , which are shown in Fig. 14 (b) and (c), respectively.

**Inter-Tile Loop Order Optimization**: The proposed data reshaping approach also achieves inter-tile data continuity by rescheduling the loop order in Fig. 5. The loop order of 1, 2, and 3 in Fig. 5 (a) does not have data dependency. Based on our data layout, we move loop 3 to the outermost loop so that the output features share similar memory access patterns in FP/BP and WU. The loop order of off-chip data transmission in FP/BP is shown in Fig. 15 (a). As shown in Fig. 12 and Fig. 13, in FP/BP, tiles of input features are fetched in the **X** direction first to generate the first output features tile. Then the tiles of output features are generated and stored in the **Y**

direction first, so the input features tiles movement follows the **Y** direction as well. Then the output features tiles are generated and stored in the **X** direction, and the access pattern of input features repeats  $\lceil \frac{M}{Tm} \rceil$  times. The burst length of output features in the OUT DMA channel is  $M^i \times R^i \times C^i$ .

The loop order in Fig. 15 (b) is adopted in WU. From Fig. 12 and Fig. 13, tiles of both input features and output features are fetched and stored in the **Y** direction first to calculate weights gradients for the first tile. Then weights are updated along the input channel dimension, so the input features tiles move in the **X** direction, while the output features access pattern (the dashed box in Fig. 12 (c)) repeats  $\lceil \frac{N}{Tn} \rceil$  times. After that, weights are updated along the output channel dimension, so the output features tiles move in the **X** direction, while the input features access pattern (the dashed box in Fig. 13 (c)) repeats  $\lceil \frac{N}{Tn} \rceil$  times. The burst length of output features in the OFM DMA channel is  $Tm \times R^i \times C^i$ . When the IFM buffer and the OFM buffer are large enough to hold the  $Tn \times R^i = in \times C^i = in$  input and  $Tm^i \times R^i \times C^i$  output features, i.e.  $R^i \leq Tr^i$ , the output features do not need to be repeatedly loaded. The loop order can be optimized as shown in Fig. 15 (c).

## 4.3 Weight Reuse in Mini-batch Training

Based on the above-mentioned optimization, we further reduce DRAM data access by reusing weights in minibatch training. Different from inference, training involves processing a batch of data at once, so data reuse is necessary to decrease the transmission times of weights between on-chip buffer and off-chip memory. On FPGAs, a BRAM bank size is large enough to store multiple tiles of weights. Therefore, we propose a weight reuse strategy based on our data layout. Thanks to our loop order shown in Fig. 15, we can load weights only when the accelerator processes the output feature tile lying in the first row. As illustrated in Fig. 16, when the accelerator processes a tile of features in the first row of the first image in a batch,  $M^i_{\ on} \times N^i \times K^i \times K^i$  weights are loaded and stored in the WEI double buffers, where  $M^i_{\ on}$  is the multiple of Tm depending on the on-chip BRAM resources. After the first  $M^i_{\ on}$  channels of OFMs in the image are processed, the first  $M^i_{\ on}$  channels of OFMs of the next image will be processed, so weights do not need to be uploaded again. The next  $M^i_{\ on}$  channels of the first image will be processed after the first  $M^i_{\ on}$  channels of all images in the batch are processed. Therefore, weights do not need to be transmitted back and forth. After the above-mentioned steps, the burst length is  $M^i \times N^i$  for FP/WU and  $Tm \times M^i_{\ on'}$  for BP, which are illustrated in Fig. 16 (b) and (c) respectively.

In mini-batch training, weight reuse will not affect the burst length of output features in WU and input features. For output features in FP and BP, after the first  $M^i$ \_on channels of OFMs of the first image are transmitted to DRAM, the next image of the batch will be processed before other channels of the prior image. Therefore, as shown in Fig. 17, the burst length is  $M^i$ \_on  $\times R^i \times C^i$ .

## 5 PERFORMANCE AND RESOURCE MODEL

In this section, we establish an analytic model to calculate the latency and resources for our design. Unlike previous works [10, 38] which only focused on the performance of a bare accelerator running on separate Conv layers, our model considers the discontinuity of off-chip memory access in a realistic end-to-end training process. Based on the model, we build a scheduling tool to determine design parameters for given FPGA devices and given network models.

#### 5.1 Performance Model

For a  $[M^i, N^i, R^i, C^i, K^i, K^i, S^i]$  Conv layer i, we assume the parameters of a tile is  $[Tm, Tn, Tr^i, Tc^i]$ . Tm and Tn are fixed for all layers since they are determined by the number of DSPs, while  $Tr^i$  and  $Tc^i$  are adjustable according to different layer parameters. In our design, Tm = Tn, and  $Tc^i = C^i$ . The computation latency of a tile of features in FP, BP, and WU can be represented as  $t^i_{COMP} = Tr^i \times Tc^i \times K^i \times K^i$  clock cycles.

The continuity of memory address significantly impacts the off-chip communication efficiency. To consider the memory access discontinuity, we assume the start time of the DMA stream is  $t_{start}$ . When discontinuity happens, DMA restarts. We have tested the start time on both the PYNQ-Z1 and the ZCU102 board, and  $t_{start} \approx 400$  cycles under 100MHz clock. We determine the data width parameters p to model the off-chip/on-chip communication bandwidth. For 32-bit floating-point, if the DMA stream width is 128 bits, p = 4. Since the burst length of input features equals the size of a tile, discontinuity happens every time a tile of input features are fetched. The latency of loading a tile of input features is formulated as  $t^i_{IFM} = t_{start} + \lceil \frac{Tn}{p} \rceil \times ((Tr^i - 1) \times S^i + K^i) \times ((Tc^i - 1) \times S^i + K^i)$  clock cycles. The weights loading latency can be represented as  $t^i_{WEI} = \lceil \frac{Tm \times Tn}{p} \rceil \times K^i \times K^i$  clock cycles, and the latency of storing a tile of output features is formulated as  $t^i_{OUT} = \lceil \frac{Tm}{p} \rceil \times Tr^i \times Tc^i$  clock cycles.  $t_{start}$  is added to  $t^i_{WEI}$  and  $t^i_{OUT}$  only when the discontinuity happens, which will be discussed in detail as follows. We define  $t^i_{LOAD} = \max\left\{t^i_{IFM}, t^i_{WEI}\right\}$ ,  $t^i_{PROD1} = \max\left\{t^i_{IFM}, t^i_{COMP}\right\}$ ,  $t^i_{PROD2} = \max\left\{t^i_{LOAD}, t^i_{COMP}\right\}$ , and  $t^i_{IFM} = \max\left\{t^i_{IFM}, t^i_{WEI}\right\}$ . and  $t_{STORE}^i = \max \left\{ t_{COMP}^i, t_{OUT}^i \right\}$ .

We assume in layer i,  $M^i$  on  $\times Tn \times K^i \times K^i$  weights are stored on-chip. If the batch size is B, weights will be loaded only during the iteration when the proposed accelerator processes the first image in the batch. For other iterations, the latency of processing  $M^i$  on channels of an image in FP can be formulated as follows.

$$Lat1^{i} = \lceil \frac{N^{i}}{Tn} - 1 \rceil \times t_{PROD1}^{i} + t_{IFM}^{i} + t_{COMP}^{i}$$

(15)

$$Lat2^{i} = \lceil \frac{N^{i}}{Tn} - 1 \rceil \times t_{PROD1}^{i} + t_{IFM}^{i} + t_{STORE}^{i}$$

(16)

$$Lat3^{i} = \left( \left\lceil \frac{M^{i}\_on}{Tm} \right\rceil \times \left\lceil \frac{R^{i}}{Tr^{i}} \right\rceil - 1 \right) \times Lat2^{i} + Lat1^{i} + t_{OUT}^{i} + t_{start}^{i}$$

(17)

Weights need to be loaded when our accelerator processes the first image in the mini-batch. In FP,  $t_{start}$  can be neglected in weight transmission since the burst length equals the size of weights, which means the addresses are continuous during the whole Conv layer. Therefore, the latency of the proposed accelerator processing  $M^i$  on channels of the first image can be formulated as follows.

$$Latb1^{i} = \lceil \frac{N^{i}}{Tn} - 1 \rceil \times t_{PROD2}^{i} + t_{LOAD}^{i} + t_{COMP}^{i}$$

(18)

$$Latb2^{i} = \lceil \frac{N^{i}}{T_{n}} - 1 \rceil \times t_{PROD2}^{i} + t_{LOAD}^{i} + t_{STORE}^{i}$$

$$\tag{19}$$

$$Latb1^{i} = \lceil \frac{N^{i}}{Tn} - 1 \rceil \times t^{i}_{PROD2} + t^{i}_{LOAD} + t^{i}_{COMP}$$

$$Latb2^{i} = \lceil \frac{N^{i}}{Tn} - 1 \rceil \times t^{i}_{PROD2} + t^{i}_{LOAD} + t^{i}_{STORE}$$

$$Latb3^{i} = \lceil \frac{M^{i}\_on}{Tm} \rceil \times \lceil \frac{R^{i}}{Tr^{i}} - 1 \rceil \times Lat2^{i} + \lceil \frac{M^{i}\_on}{Tm} - 1 \rceil \times Latb2^{i} + Latb1^{i} + t^{i}_{OUT} + t^{i}_{Start}$$

$$(20)$$

The latency of our accelerator processing the whole Conv layer in FP is formulated in Eq. (21).

$$Lat^{i} = \lceil \frac{M^{i}}{M^{i}\_on} \rceil \times ((B-1) \times Lat3^{i} + Latb3^{i}). \tag{21}$$

In BP, the situation is similar to that in FP, except that the addresses of weights are discontinuous after  $M^{i}$ \_on channels. The accelerator loads  $M^i$ \_on  $\times Tn \times K^i \times K^i$  weights together when processing the first tile of the first image, so it costs  $t_{WEI}^i = \lceil \frac{M^i \_on \times Tn}{p} \rceil \times K^i \times K^i + t_{start}^i$  clock cycles.  $Lat1^i$ ,  $Lat2^i$ ,  $Lat3^i$ ,  $Lat2^i$ ,  $Latb1^i$ , and  $Latb2^i$

remain unchanged, while  $Latb3^i = (\lceil \frac{M^i = on}{Tm} \rceil \times \lceil \frac{R^i}{Tr^i} \rceil - 1) \times Lat2^i + Latb1^i + t^i_{OUT} + t^i_{start}$ . In WU, loss features are loaded from the off-chip memory to the OFM buffer. Transmitting a tile of loss features costs  $t^i_{OFM} = t^i_{start} + Tr^i \times Tc^i \times \lceil \frac{Tm}{p} \rceil$  clock cycles. Weights are updated after all the gradients of the batch are accumulated, so transmitting the updated weights costs the same time as loading weights, which means

$t_{OUT}^i = t_{WEI}^i$ . Same with FP,  $t_{start}$  can be neglected when calculating  $t_{WEI}^i$ . We define  $t_{LOAD}^i = \max \left\{ t_{IFM}^i, t_{OFM}^i \right\}$ ,  $t_{PROD1}^i = \max\left\{t_{LOAD}^i, t_{COMP}^i\right\}, t_{PROD2}^i = \max\left\{t_{IFM}^i, t_{COMP}^i\right\}, \text{ and } t_{STORE}^i = \max\left\{t_{COMP}^i, t_{OUT}^i\right\}.$  The latency of WU of the *i*th Conv layer is formulated as follows.

$$Lat1^{i} = \lceil \frac{R^{i}}{Tr^{i}} - 1 \rceil \times t_{PROD1}^{i} + t_{LOAD}^{i} + t_{COMP}^{i}$$

(22)

$$Latb1^{i} = \lceil \frac{R^{i}}{Tr^{i}} - 1 \rceil \times t_{PROD1}^{i} + t_{LOAD}^{i} + t_{STORE}^{i}$$

(23)

$$Lat^{i} = (((B-1) \times \lceil \frac{M^{i}\_on}{Tm} \rceil \times \lceil \frac{N^{i}}{Tn} \rceil + 1) \times Lat1^{i} + (\lceil \frac{M^{i}\_on}{Tm} \rceil \times \lceil \frac{N^{i}}{Tn} \rceil - 1) \times Latb1^{i} + t_{OUT}^{i}) \times \lceil \frac{M^{i}}{M^{i}\_on} \rceil$$

(24)

As illustrated in Fig. 15 (c), when  $R^i \leq Tr^i$ , the output features do not need to be repeatedly loaded. Under this circumstance, the latency of WU is formulated as follows.

$$Lat1^{i} = \lceil \frac{N^{i}}{Tn^{i}} - 1 \rceil \times t_{PROD2}^{i} + t_{LOAD}^{i} + t_{COMP}^{i}$$

(25)

$$Latb1^{i} = \lceil \frac{N^{i}}{Tn^{i}} - 1 \rceil \times (t_{PROD2}^{i} + t_{OUT}^{i}) + t_{LOAD}^{i} + t_{COMP}^{i} + t_{OUT}^{i}$$

$$Lat^{i} = \lceil \frac{M^{i}}{M^{i}\_on} \rceil \times \lceil \frac{M^{i}\_on}{Tm} \rceil \times ((B-1) \times Lat1^{i} + Lat1b^{i})$$

(26)

$$Lat^{i} = \lceil \frac{M^{i}}{M^{i} on} \rceil \times \lceil \frac{M^{i} on}{Tm} \rceil \times ((B-1) \times Lat1^{i} + Lat1b^{i})$$

(27)

#### Resource Model 5.2

For Conv layers, the on-chip resources that need to be considered for Conv layers include DSPs and BRAMs. For DSPs,  $Tm \times Tn$  MAC operations are conducted in parallel. Therefore, the computation constraint is shown in Eq. (28), where q is the factor depending on data types. On Xilinx FPGAs, each MAC utilizes 5 DSPs for 32-bit floating-point, so q = 5 in the proposed design. In terms of on-chip memory, we select double buffers to load and store data and conduct Conv operations in parallel. The number of BRAM banks for each IFM buffer and OFM buffer are shown in Eq. (29) and Eq. (30) respectively. The notation BITs is the data bit-width adopted in the design. For the Weight buffer, we place  $M^i$ \_on $\times N^i$  kernels together for weight reuse. These data are scattered in double buffers. The number of BRAM banks for one Weight buffer is shown in Eq. (31). The on-chip memory constraint is shown in Eq. (32).

$$D_{Conv} = q \times Tm \times Tn < total DSPs number$$

(28)

$$B_{IFM} = \max_{i} B_{IFM}^{i} = \max_{i} \left\{ Tn \times \left\lceil \frac{((Tr^{i} - 1) \times S^{i} + K^{i}) \times ((Tc^{i} - 1) \times S^{i} + K^{i}) \times BITs}{Size \ of \ a \ BRAM \ Bank} \right\rceil \right\}$$

(29)

$$B_{OFM} = \max_{i} B_{OFM}^{i} = \max_{i} \left\{ Tm \times \lceil \frac{Tr^{i} \times Tc^{i} \times BITs}{Size \ of \ a \ BRAM \ Bank} \rceil \right\}$$

(30)

$$B_{OFM} = \max_{i} B_{OFM}^{i} = \max_{i} \left\{ Tm \times \lceil \frac{Tr^{i} \times Tc^{i} \times BITs}{Size \ of \ a \ BRAM \ Bank} \rceil \right\}$$

$$B_{WEI} = \max_{i} B_{WEI}^{i} = \max_{i} \left\{ Tm \times Tn \times \lceil \frac{K^{i} \times K^{i} \times \lceil \frac{N^{i}}{2 \times Tn} \rceil \times \lceil \frac{M^{i} - on}{Tm} \rceil \times BITs}{Size \ of \ a \ BRAM \ Bank} \rceil \right\}$$

(30)

$$B_{Conv} = 2 \times (B_{IFM} + B_{OFM} + B_{WEI}) < total BRAMs number$$

(32)

It should be noted that in realistic end-to-end system design, the boundary of  $D_{Conv}$  and  $B_{Conv}$  should be slightly smaller than the total DSPs and BRAMs numbers. It is because except for the MAC operations, several operations also take up a small fraction of on-chip resources. For example, some non-Conv layers (e.g. maximum pooling, average pooling, ReLU, etc.), which are inevitable in practical end-to-end training processes need extra DSPs to make comparisons and extra BRAMs to buffer the indexes. Besides, some neural networks have irregular weights kernel shapes for different Conv layers. Adding an extra buffer to fetch a tile of weights from the on-chip Weight buffer to the Conv Kernel can relieve the routing congestion in realistic FPGA implementation. Besides, since FP, BP, WU have different loop orders, extra DSPs are utilized to calculate BRAM addresses under different layer parameters. This address calculation is much more complex than that in inference. Therefore, in practical design, the estimated boundary of the on-chip resources should be set lower than the available resources empirically. The details will be further explained in Section 5.3.

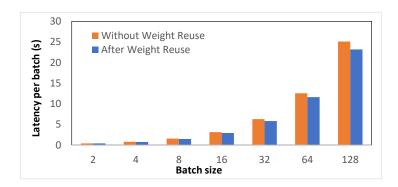

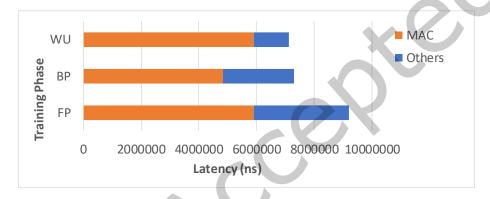

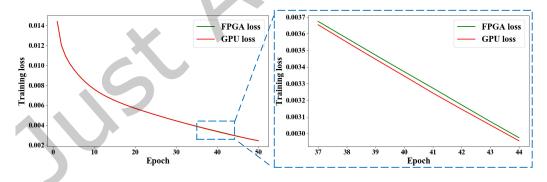

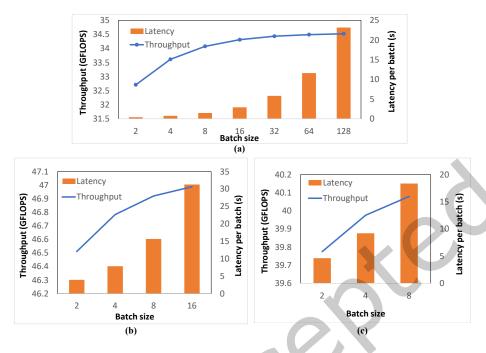

## 5.3 Computation and Memory Resources Scheduling Tool